Accelerate Your Time-to-Market for RISC-V & Image Processors

Accelerate your product launch with our advanced RISC-V and Image Processing solutions

Finding Specialized and Trained Engineers In the Semiconductor Industry?

Teaming up with fabless SoC firms, we offer RISC-V verification and design services, alongside Image Signal Processing expertise. Our team of highly skilled professionals helps you scale your design, verification, and compiler units by providing the necessary resources.

How can I accelerate my time to market?

At 10xEngineers, we specialize in expediting your product’s journey to market. By deploying exceptional design verification engineers and providing top-tier training and experience from industry giants like Digital Alpha Processor, HP, Intel, and Qualcomm, we ensure your product reaches its destination faster than ever before.

Why should I prioritize accelerating time to market?

Accelerating time to market offers several key advantages, including gaining a competitive edge over market competitors, achieving a significant reduction in overall product costs, and optimizing time by shortening the design and manufacturing cycle.

How does 10xEngineers achieve faster time to market?

We have a seasoned team led by management trained at renowned companies and armed with the expertise to identify and foster high-caliber global talent. 10xEngineers excels in surpassing the demanding standards of the semiconductor industry. By leveraging this expertise, we provide the resources and support necessary to shorten your product’s journey to market.

Our Services

Image Signal Processing

- ISP Expertise: Stay ahead with our focus on crafting unconventional image signal processors, ensuring your business remains at the forefront of technological innovation.

- Advanced Technology Integration: Harness the power of AI and computational photography breakthroughs incorporated into our designs for highly efficient image processing algorithms.

- Swift Market Entry: Access our pool of highly skilled resources specialized in Image Signal Processing (ISP) design, development, and testing, expediting your product's time-to-market.

- Stringent Quality Assurance: Rest assured knowing that each algorithm undergoes rigorous testing to meet the highest quality standards, ensuring optimal performance and reliability.

- Comprehensive R&D Support: Benefit from our all-inclusive suite of research, design, and development services aimed at elevating image quality within computational constraints. Transform your innovative concepts into high-performing, tangible products with our expertise.

RISC-V

- Expert RISC-V Services: We offer specialized RISC-V services tailored to ensure the successful delivery of complex projects within your specified timeline.

- Comprehensive Expertise: Benefit from our in-depth knowledge and proficiency in various aspects of RISC-V design, including functional and code coverage, test plan development, test generators, regression, and automation.

- Streamlined Processes: Experience seamless project execution through our efficient workflows and methodologies, designed to optimize the verification and design process for enhanced productivity and results.

- Enhanced Quality Assurance: Our meticulous attention to detail and rigorous testing procedures guarantee the highest levels of quality and reliability in your RISC-V projects.

- Compiler and LLVM Integration: Leverage our expertise in compiler and LLVM integration to unlock new possibilities and capabilities for your RISC-V designs, ensuring compatibility and efficiency across the board.

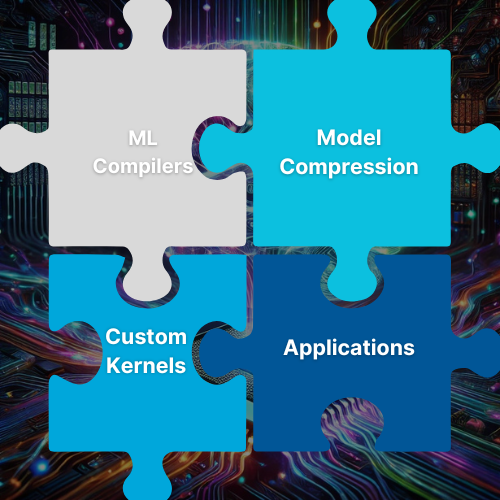

Compiler Services for AI Acceleration

Explore Full Potential of AI on Custom and Standard Hardware

Leverage our full-stack AI expertise—from compilers to applications—to accelerate generative AI and computer vision workloads. Our MLIR and LLVM-based compiler solutions are purpose-built to optimize model inference on custom hardware, including RISC-V and bespoke architectures.

We specialize in:

- ML compiler development using MLIR and LLVM for RISC-V and custom silicon

- Hardware-specific bare-metal and ML kernel optimization

- Deployment-ready model compression for vision and GenAI (LLM/VLM) use cases

- End-to-end compiler tuning: custom ops, builtins, and performance passes

- Intrinsics development for low-latency execution on custom SIMD/vector designs

Let’s Build Your AI Compiler Stack!

Our Initiatives

Infinite ISP

Our Open-Source Contribution to Image Signal Processing Innovation.

Explore a rich repository of ISP algorithms, which are easily accessible on GitHub and span from Python to C to RTL to FPGA, even to ASIC design.

Cloud V

Our Robust Solution for Streamlining RISC-V Architecture Testing

Access an innovative, on-demand CI environment with diverse testing modes including Linux shell, CI/CD scripting, and QEMU modes for RISC-V development.

Clients Testimonials

Florian 'Flo' Wohlrab

Head of OpenHW Foundation

Woodpecker Technologies

Prof. David Harris

Harvey Mudd College

Reach Us

To Know More About Our Offerings

Updates & Blogs

A Comparison on Different AMBA 5 CHI Verification IPs

In today’s semiconductor world, system-on-chip (SoC) designs face a very specific challenge:

LLM Inference with Codebook-based Q4X Quantization using the Llama.cpp Framework on RISC-V Vector CPUs

We utilize QuantX [MN25], our in-house hardware-aware quantization platform, to generate a

Cloud-Based Binary Artifactory for RISC-V Software

As the RISC-V ISA evolves with new extensions, optimizing its software ecosystem