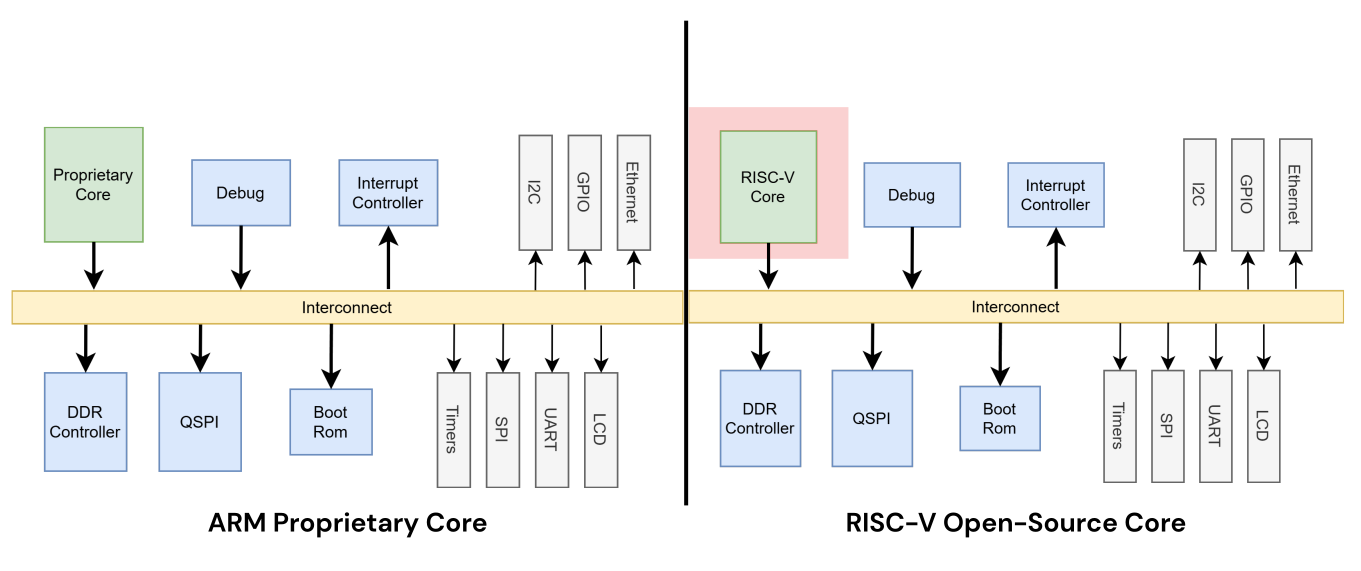

Migration from ARM to RISC-V

Replace a proprietary core with an open architecture RISC-V core

- Proprietary performance

- Open architecture

- Zero trade-offs

Open, Scalable, Efficient: RISC-V is the Future!

The futuristic RISC-V is all prepared to replace the proprietary core. Leading technology companies—including Intel, Google, NVIDIA, MediaTek, and Qualcomm are integrating their processor strategies with RISC-V. Here’s why:

| Features | ARM | RISC-V Core |

| Licensing Fees | ✔ | ✖ |

| Dependence on Vendor’s Roadmap | ✔ | ✖ |

| Customization | ✖ | ✔ |

| Vendor Independence | ✖ | ✔ |

| Features | ARM | RISC-V Core |

| Licensing Fees | ✔ | ✖ |

| Dependence on Vendor’s Roadmap | ✔ | ✖ |

| Customization | ✖ | ✔ |

| Vendor Independence | ✖ | ✔ |

Check out how we have done it:

Discovery Workshop: Your First Step Toward RISC-V Migration

Thinking about replacing your proprietary core with a RISC-V core? Before making the leap, it’s essential to assess technical feasibility and strategic fit. Our Discovery Workshop is designed to help you do just that—with clarity and confidence.

What to Expect:

System Architecture Assessment

Uncover compatibility considerations and technical hurdles specific to your current design.

Performance & Functionality Analysis

Analyze if RISC-V can match or exceed the performance of your existing core—without compromising functionality.

Customization & Optimization Opportunities

Explore how RISC-V’s open architecture can be tailored to meet your unique product goals.

Migration Roadmap & Milestones

Get a clear, phased plan for transitioning to RISC-V—minimizing disruption and aligning with your development cycles.

Why it matters:

Our experts will guide you through each step as they evaluate the viability of migration, and develop a roadmap minimizing risks while maximizing efficiency.

Take the first step toward RISC-V with confidence.

Schedule your Discovery workshop today!

Engineering-Ready Migration: The 3-Phase RISC-V Approach

Migrating from ARM to RISC-V cores is a complex and strategic initiative, often driven by the need for open architecture, cost efficiency, and long-term flexibility. Here’s how 10xEngineers support the process:

| Phase 1 | Phase 2 | Phase 3 |

| Swap RISC-V Core in an ARM SoC, with single core support | Add multi-core support to confirm smooth integration and the preservation of all functionalities | Enable ARM debugger support for RISC-V hardware by developing a hardware-level ARM-to-RISC-V debug translator. |

| Phase 1 | Swap RISC-V Core in an ARM SoC, with single core support |

| Phase 2 | Add multi-core support to confirm smooth integration and the preservation of all functionalities |

| Phase 3 | Enable ARM debugger support for RISC-V hardware by developing a hardware-level ARM-to-RISC-V debug translator. |

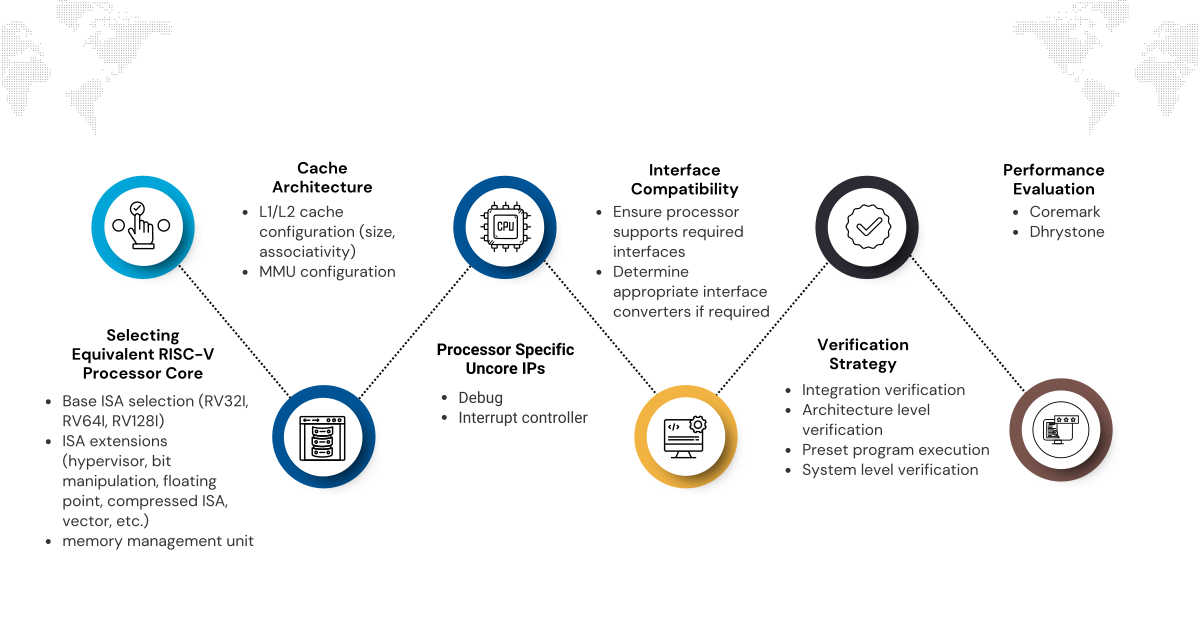

Every Step Mapped: Confidently Replace Your Processor Core with a RISC-V-Based Design

A structured, low-risk migration process — covering architecture, interfaces, verification, and performance.

Why to Choose 10xEngineers?

With ARM-to-RISC-V Migration, 10xEngineers offers a turnkey solution to replace proprietary ARM cores with open-architecture RISC-V cores. It guarantees that the migration does not sacrifice performance or functionality. We can offer you:

✓ Successful swap of single and multi-cores

✓ Integration and function verification

✓ Linux boot verification

✓ Performance analysis

✓ Enable ARM debugger support for RISC-V hardware debug

Trusted by RISC‑V International

10xEngineers is proud to be an official RISC‑V International Partner, recognized for our deep technical expertise and contributions to the RISC‑V ecosystem. 10xEngineers also serves as a maintainer for the OpenHW Foundation repositories and has made significant contributions, particularly to CVA6 and CVW.

Through our Cloud‑V platform, we became the first-ever RISC‑V Lab Partner — giving developers, product teams, and chip designers remote access to real RISC‑V hardware for testing, validation, and development.

Ready to Make the Switch?

Transform your ARM-based systems with our proven RISC-V migration solution