Next-Generation RISC-V Debug & Trace IP

Built for Deep Visibility and Faster Bring-Up

Gain complete insight into your RISC-V SoC with multi-hart debug and event-driven trace, engineered for fast bring-up, efficient validation, and confident silicon delivery.

- The Challenge

Modern RISC-V SoCs are increasingly complex—featuring multi-hart pipelines, heterogeneous cores, and multiple clock and power domains. Conventional debug solutions struggle to provide real-time visibility or scalable trace across the entire system, leading to longer bring-up cycles and higher integration risk.

- The Solution

10xEngineers Debug & N-Trace IP delivers a unified Debug + Trace solution that provides full-system visibility with low overhead and multi-hart awareness. Standards-compliant debug, real-time trace, and flexible triggering significantly reduce bring-up time and simplify system integration.

Why Choose 10xEngineers Debug & N-Trace IP?

The 10xEngineers Debug & N-Trace IP is designed to give engineering teams a complete, high-performance, and easy-to-integrate solution for debugging and tracing multi-core RISC-V SoCs—from early bring-up through post-silicon validation.

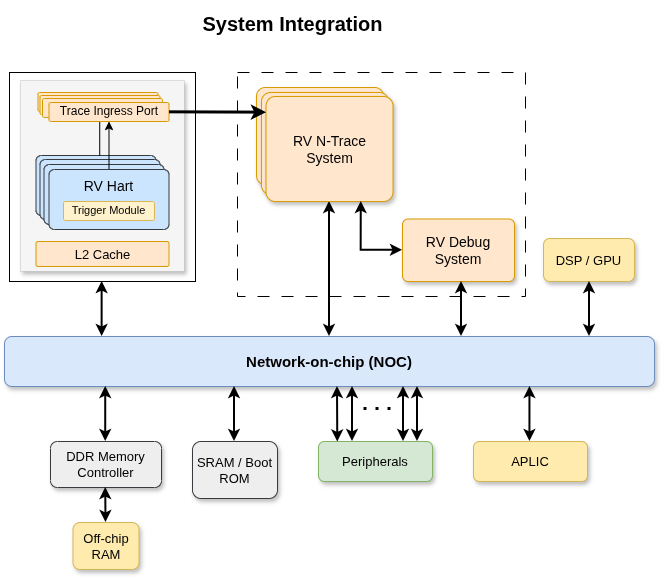

System Integration

- Specification Compliance

Fully compliant with Debug Spec v1.0 and N-Trace Spec v1.0, ensuring interoperability with standard tools and workflows.

- Full Multi-Hart Visibility

Halt, step, and inspect multiple harts simultaneously for comprehensive execution insight.

- Non-Intrusive, Real-Time Trace

Capture instruction execution with minimal impact on core performance.

- Flexible Interfaces

APB and AXI interfaces simplify configuration and access to debug and trace registers.

- Scalable Multi-Core Support

Debug and trace multiple RISC-V cores concurrently with independent control and status monitoring.

- SoC-Optimized Design

Low silicon overhead and power-efficient architecture, ideal for embedded and SoC environments.

- Optional Trigger Integration

Integrate with hardware triggers for precise, event-driven trace capture.

- Faster Development Cycles

Reduce debug iterations and simplify post-silicon validation to accelerate time to market.

- Highly Configurable

Configurable triggers, filters, and feature sets to match your SoC’s exact requirements.

- Fully Verified IP

Extensively verified to ensure predictable behavior and low integration risk.

Key Features & Benefits

- Debug Features

- Fully compliant with RISC-V Debug v1.0

- Hart groups with independent reset support

- Secure authentication and access control

- System Bus Access (SBA) for memory inspection

- External trigger support for advance debugging & event capture

- Trace Features

- IEEE-5001 Nexus standard compliance

- Support for both BTM & HTM trace modes

- Multi hart tracing with timestamp support

- On-chip & off-chip trace storage options

- Event driven trace with configurable filters and compare units

Services to Accelerate Your Development

Synthesizable RTL

High-quality Verilog/SystemVerilog IP ready for integration

Comprehensive Verification Suite

Advanced UVM testbench with coverage-driven verification

Detailed Usage Guide

Complete integration manual and architectural documentation

Assertions & Coverage Properties

Formal checks to validate integration correctness

Shell RTL & Smoke Tests

Rapid bring-up and early validation in your environment

Technical Support

Expert guidance for integration, bring-up, and debugging